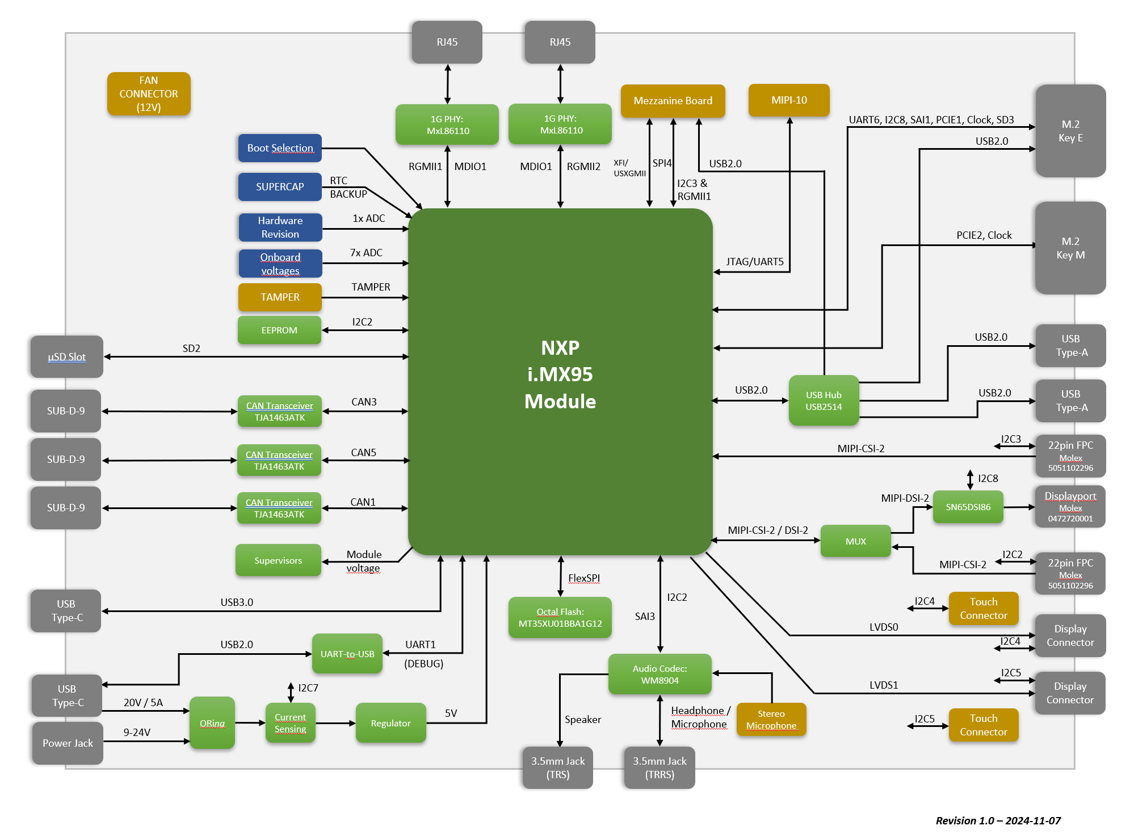

Block Diagrams

Features

| CPU | |

|---|---|

| Architecture | Arm® Cortex®-A55 |

| Processor |

|

| DRAM | 16 GByte LPDDR5 (x32) up to 6.4GT/s (w/ Inline ECC) |

| Memory | |

| SD Card | 2x (up to) interface on connector (boot source) |

| Octal-Flash | 1x Interface on connector (boot source) |

| eMMC | 1x up to 64GB (Onboard boot source) |

| EEPROM | Yes |

| Graphic | |

| Graphic | 3D GPU, OpenGL® ES 3.2, Vulkan® 1.2, OpenCL™ 3.0, 2D GPU |

| Ethernet | |

| 10GbE | 1x XFI/USXGMII |

| 1GbE | 2x RGMII |

| High Speed IO | |

| USB 3.0 | 1x |

| USB 2.0 | 1x |

| PCIe | 2x 1-lane |

| IO | |

| ADC | 1x 8ch / 12bit |

| I3C | 1x (up to) |

| CAN | 4x (up to) |

| SPI | 7x (up to) |

| FlexSPI | 1x |

| UART | 5x (up to) |

| I2C | 7x (up to) |

| Camera | |

| MIPI-CSI | 2x á 4-lane (up to) |

Our standard product versions offer what we consider to be the optimum configuration in terms of performance, price, usage and TDP. The product features lists specify the maximum range of functions per interface. However, not all interfaces or functions are always available in parallel. Flexible SERDES multiplexing is one of the reasons for this. In addition, we provide multiple memory expansion options and are also happy to accommodate specific customer wishes. So do not hesitate to contact us directly to discuss your desired configuration.

Order Info

| Name | Code | Description | Status |

|---|---|---|---|

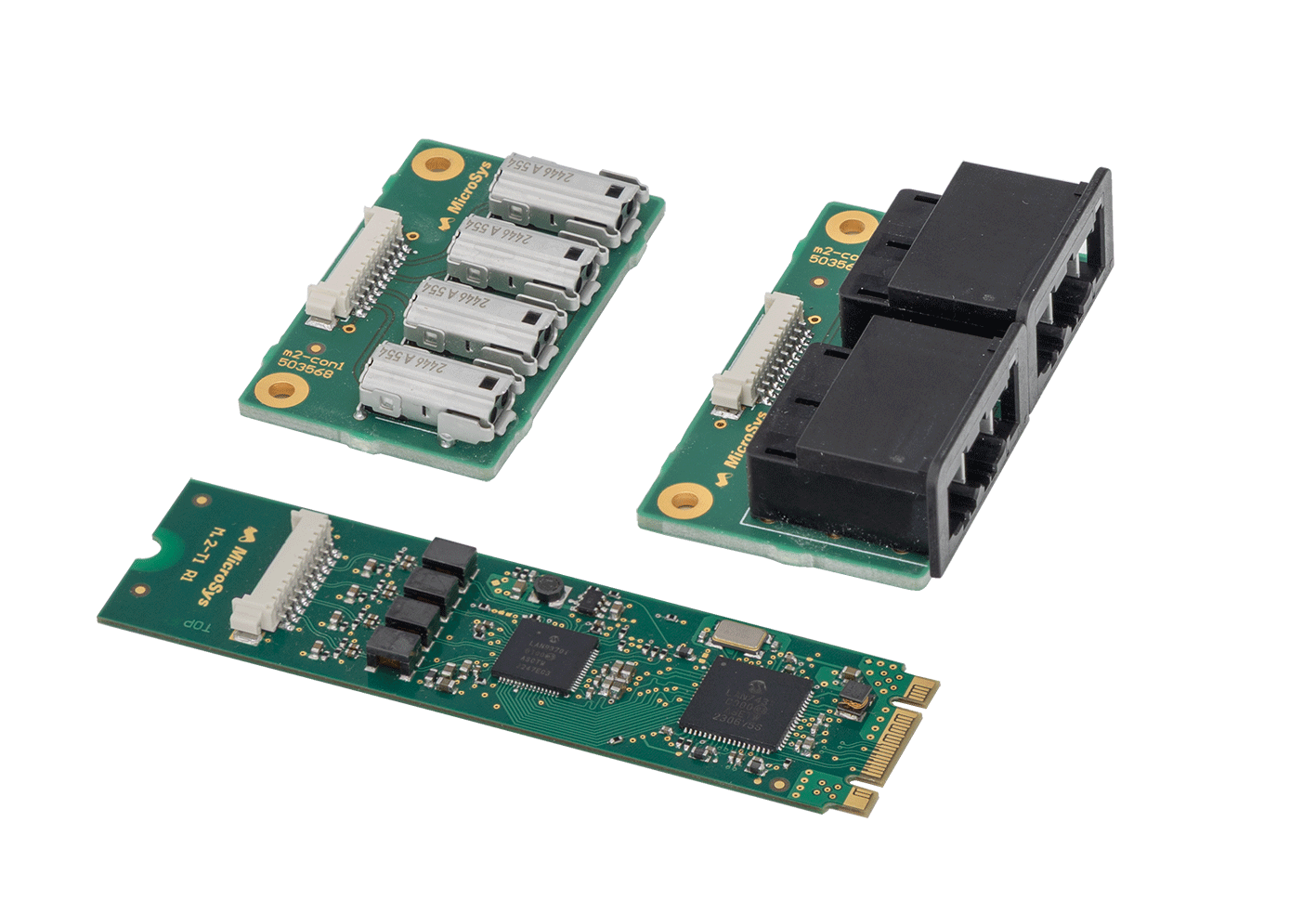

| Development Kit basic for miriac® MPX-i.MX95 | 8559xx |

|

active |

| Development Kit pro for miriac® MPX-i.MX95 | 8564xx |

|

active |