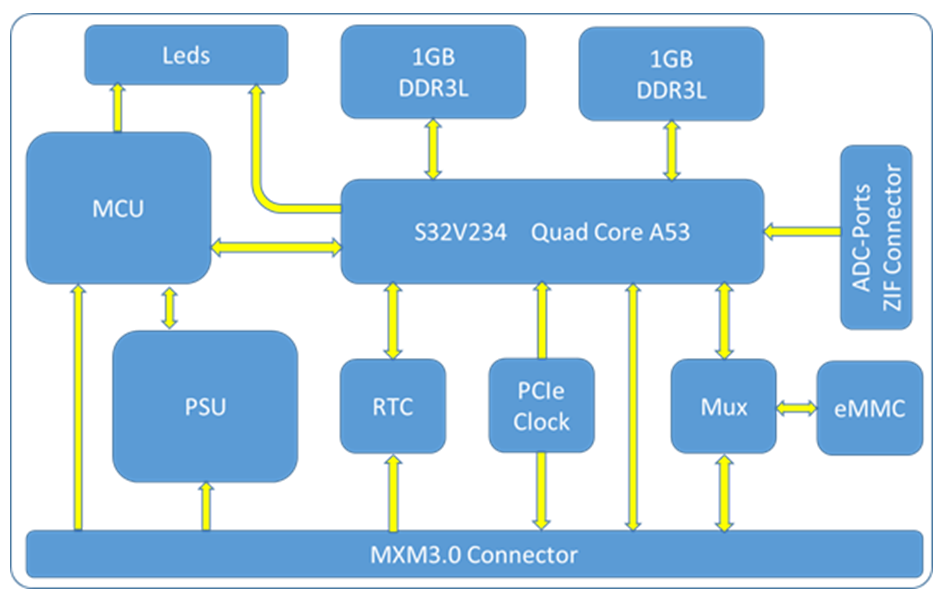

Block Diagrams

Features

| CPU | |

|---|---|

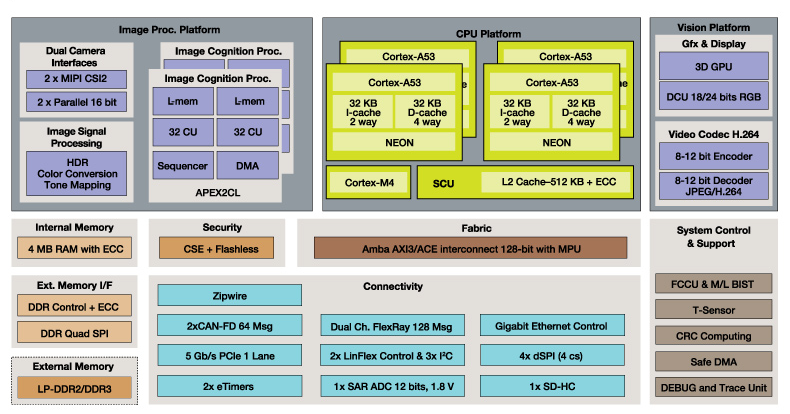

| Architecture | Arm® Cortex®-A53 |

| Processor |

NXP® S32V234 CPU:

|

| DRAM | Up to dual 1 GB 32-bit ECC DDR3L RAM |

| Memory | |

| Flash Card | USHDC: 2x 8-bit |

| Boot Flash | eMMC or external SD card |

| Graphic | |

| Graphics Controller | Yes |

| LCD Interface | 24-bit |

| HDMI Interface | Yes |

| Camera Input | Yes |

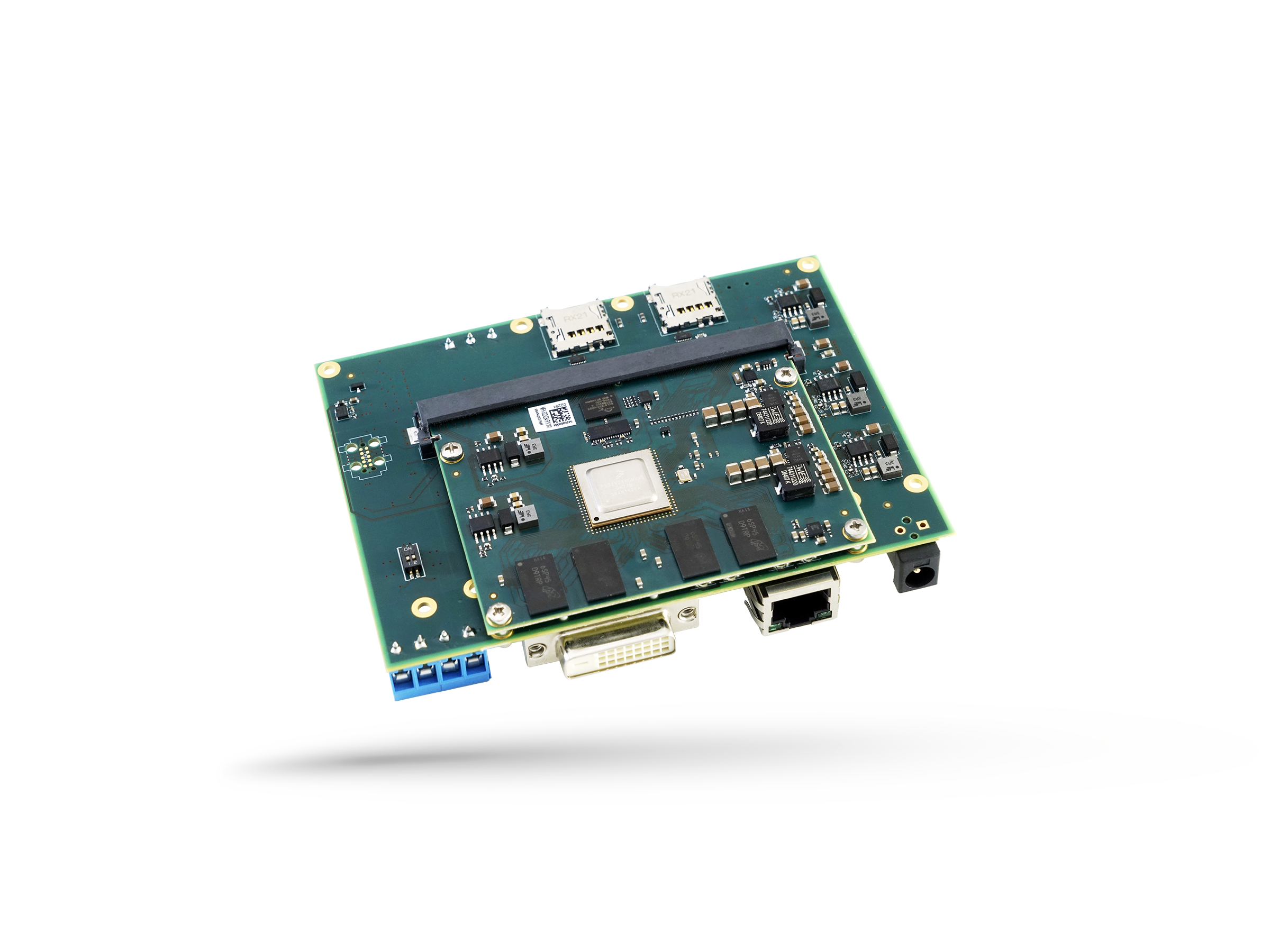

| Ethernet | |

| 1GbE | 1x |

| High Speed IO | |

| SerDes lanes | 8 |

| PCIe | PCEe Gen2 x1 (RC/EP) |

| IO | |

| UART | 2x |

| CAN FD | 2x |

| I2C | 3x |

| GPIOs | Yes |

| JTAG Debug Interface | Yes |

| Security / Safety | |

| Security | Security & Encryption: CSE-FL & AES-128 |

| Safety | FCCU and FCCU output supervision unit |

| Operating Condition | |

| Power Supply Voltage | Single +12 V DC power input (+/-25%) |

| Typical Power Consumption | 4,8 W |

| Power Management | Yes |

| RTC | PCF85263 |

| Temperature | 0 °C to 70 °C |

| Optional Extended Temperature | -40 °C to +85 °C |

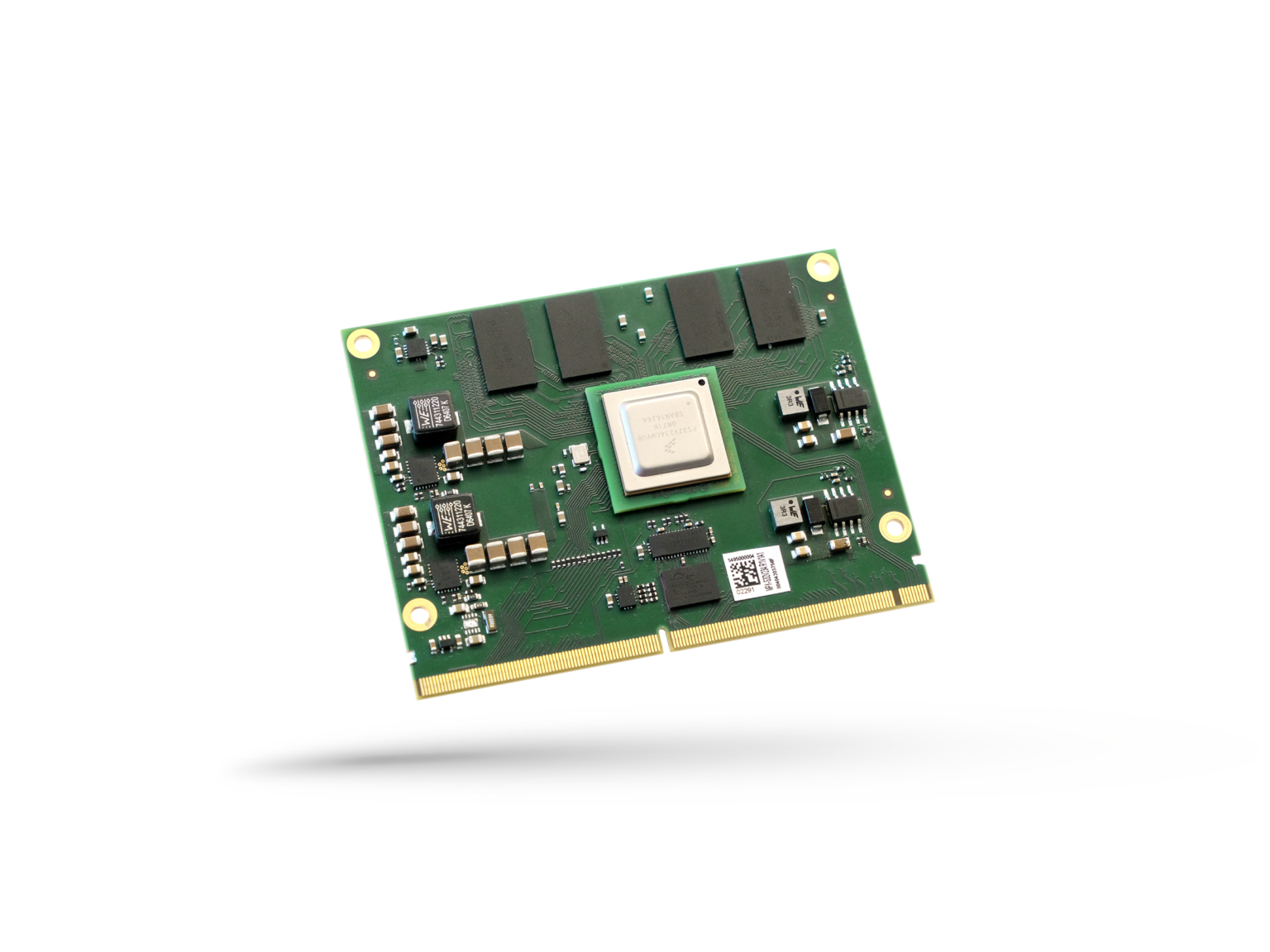

| Mechanical | |

| Dimensions | 62 mm x 82 mm |

| Connector Type | MXM3.0 |

| Software / Additional | |

| Additional |

|

Our standard product versions offer what we consider to be the optimum configuration in terms of performance, price, usage and TDP. The product features lists specify the maximum range of functions per interface. However, not all interfaces or functions are always available in parallel. Flexible SERDES multiplexing is one of the reasons for this. In addition, we provide multiple memory expansion options and are also happy to accommodate specific customer wishes. So do not hesitate to contact us directly to discuss your desired configuration.

Order Info

| Name | Code | Description | Status |

|---|---|---|---|

| miriac® MPX-S32V234 | 854901 | 4 Arm Cortex® A53, 1.0 GHz, 1 GB DDR3L w ECC, 0° to 70° C, w/o SEC | NRND |

| Development Kit basic for miriac® MPX-S32V234 | 8557xx |

|

NRND |

Downloads

FAQ

Q: In our environment, we need solutions that are available over a very long period of time (up to 15 years). How long are your modules available?

A: Using NXP CPUs on our SoMs we are able to provide an availability of 15 years from the time of the launch of the CPU. With LTB and long-time stocking we are even able to extend this period.